# Design of n-Tier Multilevel Interconnect Architectures by Using Carbon Nanotube Interconnects

Esmat Kishani Farahani, Member, IEEE, and Reza Sarvari, Member, IEEE

Abstract—In this paper, n-tier methodology is developed to design multilevel interconnect architecture of macrocells using single-wall carbon nanotube (SWCNT) bundles. Upper limit of low-bias voltage of SWCNT bundle interconnects is derived and its dependence on temperature, SWCNTs' diameter, and interconnect length is studied. Possibility of using SWCNT bundles as local interconnects at 7.5-nm technology node is discussed, and it is shown that SWCNT bundles with 1 nm diameter cannot be used at the first interconnect metal level. Using Cu and SWCNT bundles, multilevel interconnect architecture of a 7.5-nm ASIC macrocell is designed which reduces the number of metal levels by 27% and power dissipation by 25% compared with the multilevel interconnect architecture designed with only Cu. The effect of aspect ratio (AR) on the n-tier design is studied. It is shown that decreasing AR of SWCNT bundle interconnects, decreases total power dissipation of the ASIC macrocell by 41%. The impact of temperature variation on the design of multilevel interconnect architecture is also investigated.

*Index Terms*—Carbon nanotube (CNT), low-bias regime, multilevel interconnect architecture, n-tier methodology, temperature variation.

#### I. INTRODUCTION

**C** ARBON nanotubes (CNTs) are promising candidates to replace copper interconnects [1]–[3]. They have outstanding properties such as long mean-free path [4], high thermal conductivity [5], and high current-carrying capability [6] that outperform copper interconnects. One of the challenges to implement CNT bundle interconnects on chips, has been the production of dense vertical and horizontal CNT bundles with suitable lengths, widths, and thicknesses to be integrated into CMOS technologies. Fabrication of dense vertical CNT bundles as vias is reported in [7]–[9]. Although fabrication of horizontal CNT bundles is more challenging, Chiodarelli *et al.* [10] have reported their fabrication with dimensions down to 50 nm and symmetrical contacts. Moreover, dense horizontal CNT bundles over 100- $\mu$ m length are fabricated using liquid-assisted flattening technique [11].

Although technology is going toward replacing Cu interconnects with CNT bundles, there is no clear image of chips designed with CNT bundle interconnects and their differences

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2014.2360713

with the conventional chips from the viewpoint of interconnect power dissipation, repeater power dissipation, wire pitch, and number of metal levels. In this paper, n-tier methodology [12] is developed to design multilevel interconnect architectures by using CNT bundles. Maximum allowed low-bias voltage for CNT bundles is derived and the influence of temperature, CNTs' diameter, and interconnect length on the low-bias voltage is studied. Possibility of using CNT bundles as local interconnects at 7.5-nm technology node is discussed. Multilevel interconnect architecture of an ASIC logic macrocell case study for 7.5-nm technology node is designed with Cu and CNT bundles. Impact of CNT bundles' aspect ratio (AR) on the n-tier design is investigated. Multilevel interconnect architecture of the macrocell is designed for different temperatures and the results are compared.

This paper is organized as follows. In Section II, n-tier methodology is developed for CNT bundle interconnects. In Section III, upper limit of low-bias voltage for CNT bundles is derived and possibility of using CNT bundles as local interconnects for the 7.5-nm technology node is discussed. In Section IV, multilevel interconnect architecture for a 7.5-nm ASIC macrocell is designed using Cu and CNT bundles and the results are compared. In Section V, impact of CNT bundles' AR on multilevel interconnect architecture design of the macrocell is studied. In Section VI, multilevel interconnect architecture design of the macrocell is designed for different temperatures, and the impact of temperature variation on the design is discussed. Section VII concludes the paper.

## II. DEVELOPMENT OF n-TIER METHODOLOGY FOR CNT BUNDLES

In the n-tier method [12], the stochastic wire-length distribution [13] is used to design wire pitch of each tier optimally by considering area and time constrains. Two adjacent orthogonal metal levels are called a pair, and a collection of pairs with the same wire pitch is called a tier (Fig. 1). The area constrain is considered by equating available area for wiring  $A_{av}$  to required area for wiring  $A_{req}$  as [12]

$$A_{\rm av} = e_w A_m = \chi p_t \sqrt{\frac{A_m}{N_g}} \int_{L_{\rm min}^t}^{L_{\rm max}^t} li(l) dl = A_{\rm req} \qquad (1)$$

where  $e_w$  is the wiring efficiency (40%),  $A_m$  is the macrocell area,  $\chi$  is the point to point conversion factor [13],  $p_t$  is the wire pitch of *t*th pair,  $N_g$  is the number of logic gates,

1063-8210 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received November 24, 2013; revised July 11, 2014; accepted September 17, 2014.

The authors are with the Sharif University of Technology, Tehran 14588-89694, Iran (e-mail: kishani@ee.sharif.edu; sarvari@ sharif.edu).

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS

insertion of k repeaters with size s can be stated as [16]

$$\tau = 0.69 \left( \frac{R_{out}}{s} (C_{out}ks + cl + C_I sk) + \frac{R_Q + R_C}{2} (cl + 2C_I sk) + rlC_I s \right) + 0.38 \frac{rcl^2}{k}$$

(8)

where optimal number of repeaters  $k_{opt}$  and optimal repeaters' size sopt are as [16]

$$k_{\rm opt} = \sqrt{\frac{0.38}{0.69} \frac{rcl^2}{R_{\rm out}(C_{\rm out} + C_I) + (R_Q + R_C)C_Is}}$$

(9)

$$s_{\text{opt}} = \sqrt{\frac{R_{\text{out}}cl}{(R_Q + R_C)C_Ik + rlC_I}}.$$

(10)

It is seen that by replacing  $R_O + R_C$  with zero in (8) to (10),  $\tau$ ,  $k_{opt}$ , and  $s_{opt}$  of Cu interconnects are obtained.

The n-tier design starts by setting the wire pitch of the first metal pair to twice the minimum feature size of the technology. Then, maximum wire length of the pair  $L_{max}^{t}$  is calculated from (1). For the other pairs, (1)-(3) [or (8)] should be solved simultaneously to determine the wire pitch and the maximum wire length of each pair.

## III. UPPER LIMIT OF LOW-BIAS VOLTAGE FOR CNT BUNDLE INTERCONNECTS

Depending on the bias voltage applied to CNT bundle interconnects, they may work at low-bias or high-bias regime. At the low-bias regime, effective mean-free path of CNTs is limited by acoustic phonon scattering, whereas at the highbias regime, the effective mean-free path is determined by optical phonon scattering [17]. For interconnect applications, low-bias regime is of great importance because of CNTs' linear behavior and long mean-free path. To work at lowbias regime, acoustic phonon mean-free path  $\lambda_{ac}$  must be much smaller than optical phonon mean-free path  $\lambda_{opt}$  so that  $\lambda_{ac}$  becomes dominant term in determining effective meanfree path (11). This can be expressed as  $\lambda_{ac} = \gamma \lambda_{opt}$  [17] where  $\gamma$  is a criterion used to define low-bias regime, and is smaller than 1. For example, for  $\gamma = 0.1$ ,  $\gamma = 0.15$ , and  $\gamma = 0.3$ ,  $\lambda_{\text{eff}}$  is 0.91, 0.87, and 0.77 times of  $\lambda_{\text{ac}}$ , respectively. So  $\gamma = 0.1$  shows a low-bias regime well, however, by increasing  $\gamma$  the approximation of low-bias regime becomes weaker

$$\lambda_{\rm eff} = \left(\frac{1}{\lambda_{\rm ac}} + \frac{1}{\lambda_{\rm opt}}\right)^{-1}.$$

(11)

Optical phonon mean-free path is defined as [18]

$$\lambda_{\rm opt} = \left(\frac{1}{\lambda_{\rm op,abs}} + \frac{1}{\lambda_{\rm op,ems}^{\rm fld}} + \frac{1}{\lambda_{\rm op,ems}^{\rm abs}}\right)^{-1}$$

(12)

where  $\lambda_{op,abs}$  is optical phonon absorption mean-free path.  $\lambda_{op,ems}^{fld}$ , and  $\lambda_{op,ems}^{abs}$  are optical phonon emission mean-free paths due to electric field and absorption, respectively.

pair#3

Fig. 1. n-tier multilevel interconnect architecture.

$L_{\min}^{t}$  and  $L_{\max}^{t}$  are, respectively, minimum and maximum wire length of the *t*th pair in gate pitches (GPs), l is the wire length in GP, and i(l) is the interconnect density function [13]. The time constrain is considered by equating delay of the longest wire in each pair  $\tau$  to a fraction  $\eta$  (=0.9) of the clock time  $(1/f_c)$  as

$$\tau = \frac{\eta}{f_c}.$$

(2)

The delay of a CNT bundle interconnect with length lbetween two drivers with size s is as [14]

$$\tau = 0.69 \left( R_{\text{out}} C_{\text{out}} + \left( \frac{R_{\text{out}}}{s} + \frac{R_Q + R_C}{2} \right) cl + \left( \frac{R_{\text{out}}}{s} + R_Q + R_C + rl \right) C_I s \right) + 0.38 r cl^2 \quad (3)$$

where  $R_{out}$ ,  $C_{out}$ , and  $C_I$  are, respectively, the output resistance, output capacitance, and input capacitance of the drivers with minimum size, r and c are, respectively, distributed per unit length resistance and capacitance of the interconnect, and  $R_O$  and  $R_C$  are, respectively, quantum contact resistance and imperfect contact resistance of the CNT bundle

$$R_Q = \frac{12.9}{N_{\rm ch}N_{\rm CNT}} \quad [k\Omega] \tag{4}$$

$$r = \begin{cases} \frac{R_Q}{\lambda} & \text{for } l > \lambda\\ 0 & \text{for } l \le \lambda \end{cases}$$

(5)

$$c^{-1} = \left(c_q^{-1} + c_e^{-1}\right) \tag{6}$$

$$c_q = 193.7 N_{\rm ch} N_{\rm CNT} \quad [\rm pF] \tag{7}$$

where  $\lambda$  is the mean-free path of SWCNTs,  $N_{ch}$  is the number of conducting channels per each SWCNT,  $N_{\rm CNT}$  is the number of metallic SWCNTs in the bundle,  $c_e$  is the per unit length electrostatic capacitance of the bundle, and  $c_q$  is the quantum capacitance of the bundle [15]. Assuming the value of 10 k $\Omega$  as the imperfect contact resistance of each SWCNT, the imperfect contact resistance of the bundle is defined as  $R_C = 10/N_{\rm CNT}$  in k $\Omega$ .

Following a procedure similar to Cu interconnects, delay expression of a CNT bundle interconnect with length l, after

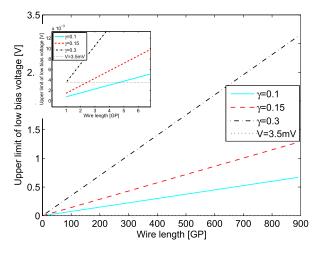

Fig. 2. Upper limit of low-bias voltage versus wire length for CNTs with 1 nm diameter and for three different criteria at room temperature. Inset: magnified plot for short-length wires.

The formulas of the mean-free paths are given in [18] that can be rewritten as

$$\lambda_{\rm ac} = 4 \times 10^5 \frac{d}{T} \tag{13}$$

$$\lambda_{\rm op,abs} = \alpha d \left( e^{\frac{\hbar\omega_{\rm op}}{K_B T}} - 1 \right) \tag{14}$$

$$\lambda_{\rm op,ems}^{\rm abs} = 2\alpha d \sinh\left(\frac{\hbar\omega_{\rm op}}{K_B T}\right) \tag{15}$$

$$\lambda_{\rm op,ems}^{\rm fld} = \frac{\hbar\omega_{\rm op} - K_B T}{q V} L + \alpha d \left( 1 - e^{-\frac{\hbar\omega_{\rm op}}{K_B T}} \right) \quad (16)$$

where *d* is the SWCNTs' diameter, *T* is the temperature,  $\hbar\omega_{op} = 0.18 \text{ eV}$ ,  $\alpha = 56.0531$ , and  $K_B$  is the Boltzmann constant. Substituting (13)–(16) in  $\lambda_{ac} = \gamma \lambda_{opt}$  and solving for *V*, upper limit of low-bias voltage is derived as

$$V_{\rm UL} = \frac{(\hbar\omega_{\rm op} - K_B T)L}{qd\left[\alpha\left(e^{-\frac{\hbar\omega_{\rm op}}{K_B T}} - 1\right) + \frac{1}{\zeta}\right]}$$

(17)

$$\zeta = 2.5 \times 10^{-6} \gamma T - \frac{e^{-\frac{\hbar\omega_{\rm op}}{K_B T}}}{2\alpha \sinh\left(\frac{\hbar\omega_{\rm op}}{2K_B T}\right)} - \frac{1}{2\alpha \sinh\left(\frac{\hbar\omega_{\rm op}}{K_B T}\right)}.$$

(18)

As (17) shows, upper limit of low-bias voltage  $V_{UL}$  is a function of wire length, SWCNTs' diameter, and temperature.  $V_{UL}$  is proportional to wire length and reciprocal of SWCNTs' diameter, whereas its dependence on temperature is not simply distinguishable.

Fig. 2 shows  $V_{\rm UL}$  versus wire length for CNTs with 1 nm diameter and for three different criteria ( $\gamma = 0.1$ , 0.15, and 0.3) at room temperature. It is seen that  $V_{\rm UL}$ increases by wire length. So, if the smallest wire length (1 GP) on a macrocell works at low-bias regime for a technology node, definitely the other wire lengths of the macrocell will work at the low-bias regime too. So we consider an 1 GP interconnect (1 GP = 0.1178  $\mu$ m for 7.5-nm technology node [19]) between two drivers and investigate its  $V_{\rm UL}$ . According to [20],

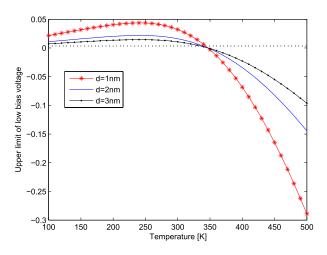

Fig. 3. Upper limit of low-bias voltage versus temperature for CNTs with 1 nm diameter and for three different criteria, L = 43 GP. Dotted line:  $V_{\text{max}} = 3.5$  mV.

maximum voltage that drops on the interconnect for the worst case is as

$$V_{\max} = \frac{(R_C + R_Q)}{(R_C + R_Q) + R_{\text{out}}} V_{\text{dd}}.$$

(19)

For a SWCNT bundle interconnect (wire pitch = 15 nm, length = 1 GP, aspect ratio = 2.1, diameter of SWCNTs = 1 nm) in the 7.5 technology node,  $R_Q = 83.8 \Omega$  and  $R_C = 130 \Omega$ , also  $R_{out} = 36.86 \text{ k}\Omega$  and  $V_{dd} = 0.61 \text{ V}$  [19] that result in  $V_{max} = 3.5 \text{ mV}$ . It is seen that  $V_{max}$  is much smaller than  $V_{dd}$  because of the significant output resistance of the drivers. Assuming only one third of the SWCNTs in the bundle to be metallic,  $V_{max}$  becomes 10.4 mV.

As the inset of the Fig. 2 shows  $V_{UL}$  of 1 GP wire length is 0.75 mV for  $\gamma = 0.1$  which is smaller than  $V_{max}$ , whereas for wire lengths larger than 4 GP,  $V_{max} < V_{UL}$ . So, we do not use CNTs for wiring the first metal pair. We also do not use two different kinds of interconnect for wiring a pair, because its implementation may be difficult technologically.

Fig. 3 shows dependence of  $V_{UL}$  on temperature for CNTs with 1 nm diameter and for three different criteria. The length of CNTs is 43 GP (minimum wire length in pair 2 according to the next section). The dotted line shows  $V_{max} = 3.5$  mV. For the temperatures that  $V_{UL}$  becomes smaller than  $V_{max}$ , the assumption of low-bias regime is not valid. In other words, this temperature range represents high-bias regime in which optical phonons determine effective mean-free path of CNTs. As Fig. 3 shows a CNT with 1 nm diameter and 43 GP length works at the low-bias regime up to temperature T = 343 and 380 K for the criteria of  $\gamma = 0.1$  and  $\gamma = 0.15$ , respectively.

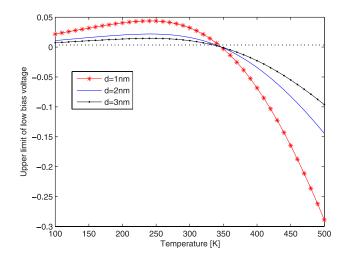

Fig. 4 shows dependence of  $V_{UL}$  on temperature for CNTs with different diameters. The wire length is 43 GP and  $\gamma = 0.1$ . It is seen that  $V_{UL}$  decreases by increasing *d*. The maximum temperature for low-bias regime for CNTs with diameters 1, 2, and 3 nm is, respectively, 343, 340, and 334 K. It is also seen that the temperature at which CNTs with different diameters cross the zero voltage, is the same.

Fig. 4. Upper limit of low-bias voltage versus temperature for CNTs with 1, 2, and 3 nm diameter,  $\gamma = 0.1$ , L = 43 GP. Dotted line:  $V_{\text{max}} = 3.5$  mV.

TABLE I Data Used From ITRS for the Case Study

| Year                                                                    | 2024                     |

|-------------------------------------------------------------------------|--------------------------|

| 1/2 wiring pitch[nm]                                                    | 7.5                      |

| Clock frequency $f_c$ [GHz]                                             | 6.234                    |

| Chip area $[cm^2]$                                                      | 8.58                     |

| Number of logic gates [millions]                                        | 61798                    |

| $V_{dd}$ [V]                                                            | 0.61                     |

| Subthreshold channel leakage current of                                 |                          |

| NMOS transistor $I_{leak}$ [nA/ $\mu$ m]                                | 100                      |

| Threshold voltage of NMOS transistor $V_{th}$ [V]                       | 0.249                    |

| Short circuit current of minimum size driver $I_{sc}$ [ $\mu A/\mu m$ ] | 65 [22]                  |

| Output resistance of minimum size driver $R_{out}$                      | $36.86 \mathrm{k}\Omega$ |

| Output capacitance of minimum size driver $C_{out}$                     | 3.45 aF                  |

| Input capacitance of minimum size driver $C_I$                          | 3.45 aF                  |

TABLE II Definition of SWCNTs and Cu Parameters

| Symbol         | Definition                                  | Value                        |

|----------------|---------------------------------------------|------------------------------|

| $\lambda$      | mean free path of SWCNTs at 300K            | $1.27 \mu m$                 |

| d              | diameter of SWCNTs                          | 1 nm                         |

| AR             | aspect ratio of interconnects               | 2.1                          |

| $\beta$        | ratio of the metallic SWCNTs to             | 1, 1/3                       |

|                | all SWCNTs in the bundle                    |                              |

| $ ho_0$        | resistivity of bulk copper (no size effect) | $2.2 	imes 10^{-8} \Omega m$ |

| $\lambda_{Cu}$ | mean free path of Cu at 300K                | 38 nm                        |

| Ref            | reflectivity coefficient of copper          | 0.5                          |

| Spec           | specularity coefficient of copper           | 0.5                          |

| LER            | line edge roughness                         | 40%                          |

# IV. DESIGN OF n-TIER INTERCONNECT ARCHITECTURE OF AN ASIC MACROCELL BY USING SWCNT BUNDLES AND Cu

In this section n-tier methodology and developed n-tier methodology are used to design multilevel interconnect architecture of a 7.5-nm ASIC macrocell case study by using Cu and SWCNT bundles. ITRS data for the 7.5-nm technology node is tabulated in Table I. As mentioned in previous section, we use Cu for the first metal pair and CNT bundles for the other pairs, to be sure of working at low-bias regime. Parameters of Cu and SWCNT interconnects at room temperature are tabulated in Table II. We have also used a fraction of optimal

TABLE III Results of n-Tier Design for a 7.5-nm ASIC Macrocell by Using SWCNT Bundles and Cu

|        | C     | ASE I     | CA       | SE II     | CAS      | E III     |

|--------|-------|-----------|----------|-----------|----------|-----------|

|        |       |           | CASE II  |           | CASE III |           |

|        |       | Cu        | Cu-SWCNT |           | Cu-SWCNT |           |

|        | LER=3 | nm (40%)  | β        | =1        | β=       | =1/3      |

| Pair's | pitch | $L_{max}$ | pitch    | $L_{max}$ | pitch    | $L_{max}$ |

| number | [nm]  | [GP]      | [nm]     | [GP]      | [nm]     | [GP]      |

| 1      | 15    | 42        | 15       | 42        | 15       | 42        |

| 2      | 15    | 842       | 15       | 842       | 15       | 842       |

| 3      | 24.7  | 4706      | 18.1     | 9273      | 21.6     | 6100      |

| 4      | 49.1  | 12202     | 51       | 31083     | 49.6     | 16650     |

| 5      | 84.7  | 25240     | 128.5    | 82863     | 101.8    | 36692     |

| 6      | 191.8 | 70084     |          |           | 221.4    | 82863     |

| 7      | 220.7 | 82863     |          |           |          |           |

TABLE IV Comparison of Power Dissipation and the Number of Required Metal Pairs in n-Tier Design of a 7.5-nm ASIC Macrocell by Using SWCNT Bundles and Cu

|                 | CASE I         | CASE II   | CASE III      |

|-----------------|----------------|-----------|---------------|

|                 | Cu             | Cu-SWCNT  | Cu-SWCNT      |

|                 | LER=3 nm (40%) | $\beta=1$ | $\beta = 1/3$ |

| Number of pairs | 6.0008         | 4.3752    | 5.3449        |

| $P_{int}[W]$    | 33.6206        | 33.6213   | 33.621        |

| $P_{rep}[W]$    | 59.8058        | 36.5135   | 31.1319       |

| $P_{sc}[W]$     | 0.1026         | 0.0626    | .0534         |

| $P_{leak}[W]$   | 37.7132        | 23.0252   | 19.6316       |

| $P_{dyn}[W]$    | 21.99          | 13.4257   | 11.4469       |

| $P_{tot}[W]$    | 93.4264        | 70.1348   | 64.7528       |

number of repeaters  $\xi = 0.4$  to decrease power dissipation, in the cost of larger delay.

Power dissipation of the interconnects and repeaters are defined as [21], [22]

$$p_{\rm int} = \frac{1}{2} \alpha c l V_{\rm dd}^2 f_c \tag{20}$$

$$p_{\rm rep} = p_{\rm dyn} + p_{\rm sc} + p_{\rm leak} \tag{21}$$

$$p_{\rm dyn} = \frac{1}{2} \alpha (C_{\rm out} + C_I) s V_{\rm dd}^2 f_c \tag{22}$$

$$p_{\text{leak}} = \frac{5}{2} V_{\text{dd}} I_{\text{leak}} w_{\min} s \tag{23}$$

$$p_{\rm sc} = \alpha t_{\rm sc} V_{\rm dd} I_{\rm peak} f_c = \alpha t_{\rm sc} V_{\rm dd} I_{\rm sc} w_{\rm min} s f_c \qquad (24)$$

$$t_{\rm sc} \approx \frac{V_{\rm dd} - 2V_{\rm th}}{V_{\rm dd}} \times \frac{0.69C_{\rm out}R_{\rm out}}{0.8}$$

(25)

where  $p_{int}$  is the switching power dissipation of an interconnect with length l,  $\alpha$  is the switching factor and is assumed to be 0.05,  $p_{rep}$  is the power dissipation of a repeater and is consisted of short-circuit power dissipation  $p_{sc}$ , leakage power dissipation  $p_{leak}$ , and dynamic power dissipation  $p_{dyn}$ ,  $w_{min}$  is the minimum feature size of the technology,  $I_{leak}$  is the subthreshold channel leakage current of nMOS transistor and it is assumed to be larger than the gate and junction leakage currents [19], and  $t_{sc}$  is the time that both nMOS and pMOS transistors are on.

Tables III and IV show results of the n-tier design for three different cases. In all cases, wires have AR = 2.1. In CASE I, all pairs are designed with Cu. In CASE II and CASE III, pair 1 is designed with Cu and the other pairs are designed with SWCNT bundles. In CASE II,  $\beta = 1$ , whereas FARAHANI AND SARVARI: DESIGN OF n-TIER MULTILEVEL INTERCONNECT ARCHITECTURES

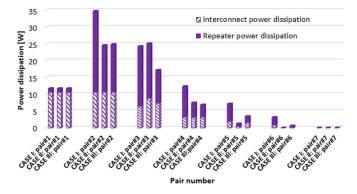

Fig. 5. Power dissipation versus pair number for the three cases.

in CASE III,  $\beta = 1/3$ .  $L_{\text{max}}$  represents maximum wire length in each pair.  $P_{int}$ ,  $P_{sc}$ ,  $P_{leak}$ , and  $P_{dyn}$  are interconnect power dissipation, short-circuit power dissipation, leakage power dissipation, and dynamic power dissipation of the macrocell, respectively. Prep represents repeater power dissipation of the macrocell and is defined as  $P_{rep} = P_{sc} + P_{leak} + P_{dyn}$ . Total power dissipation of interconnects and repeaters is defined as  $P_{\text{tot}} = P_{\text{int}} + P_{\text{rep}}$ . It is seen that use of SWCNT bundles decreases the number of metal pairs, and the total power dissipation dramatically. CASE II and CASE III in comparison with CASE I show 27% and 11% reduction in the number of metal pairs, and 25% and 30% reduction in total power dissipation, respectively. Difference in power dissipation between the cases is mainly due to the difference in repeater power dissipation for which size and number of repeaters are different [refer to (22)-(24)]. Moreover, more than 60% of repeater power dissipation is due to the leakage power dissipation.

Fig. 5 shows power dissipation versus pair number for the three cases. Pair 1 of the all cases is designed with Cu, hence no difference is seen between the cases. In pair 2, the cases have equal interconnect power dissipation, because the wire pitch, minimum wire length, and maximum wire length of the cases are similar. However, their repeater power dissipations are different owing to the difference in the number of repeaters k and repeater sizes s. It is inferred from (9)and (10) that CASE II in Comparison with CASE III has smaller number of repeaters and larger repeater sizes (because r and  $R_O + R_C$  are smaller in CASE II in comparison with CASE III). The product of  $s \times k$  is also larger in CASE III in comparison with CASE II that leads to larger repeater power dissipation. Repeater power dissipation of CASE I is very high in comparison with CASE II and CASE III, because of the larger product of  $s \times k$ . It is worthy to note that because of the nonzero value of  $R_Q + R_C$  in the denominator of  $s_{opt}$  and  $k_{\text{opt}}$  for the CNT bundles, the product of  $s \times k$  is smaller in comparison with Cu wires. In pair 3, the cases have different wire pitches that leads to different number of wires, interconnect power dissipations, and repeater power dissipations. CASE II in comparison with CASE III has larger interconnect and repeater power dissipation because of having larger  $L_{max}$ (Table III). For the other pairs of the cases, increasing the pair number, increases the wire pitch which causes decrease in the average wire length and consequently the interconnect

TABLE V IMPACT OF SWCNT BUNDLES' AR ON n-TIER DESIGN FOR THE 7.5-nm ASIC MACROCELL

|        |       | WCNT      |       | WCNT      |       | WCNT      |

|--------|-------|-----------|-------|-----------|-------|-----------|

|        | AR    | =0.5      |       | R = 1     | AR    | = 2.1     |

| Pair's | pitch | $L_{max}$ | pitch | $L_{max}$ | pitch | $L_{max}$ |

| number | [nm]  | [GP]      | [nm]  | [GP]      | [nm]  | [GP]      |

| 1      | 15    | 42        | 15    | 42        | 15    | 42        |

| 2      | 15    | 842       | 15    | 842       | 15    | 842       |

| 3      | 21    | 6486      | 19.3  | 7839      | 18.1  | 9273      |

| 4      | 49.7  | 18035     | 49.1  | 23822     | 51    | 31083     |

| 5      | 108   | 41948     | 160.4 | 82863     | 128.5 | 82863     |

| 6      | 207.3 | 82863     |       |           |       |           |

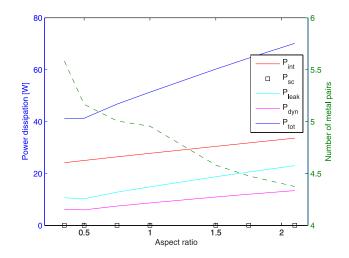

Fig. 6. Power dissipation (left axis) and number of required metal pairs (right axis) versus AR.

power dissipation. The repeater power dissipation also decreases, because although the product of  $s \times k$  increases, the number of wires decreases according to the wire density function.

#### V. DEPENDENCE OF n-TIER DESIGN ON AR

An important feature of CNT bundle interconnects is their current-carrying capability which is three orders of magnitude larger than Cu interconnects [6]. So, one may decrease the AR of interconnects by using SWCNT bundles. This decreases capacitance per unit length of the interconnects and consequently the interconnect power dissipation. However, by decreasing AR, resistance per unit length of the interconnects increases, which may increase wire pitch of the pairs, and number of the metal pairs.

Table V shows the results of the n-tier design for the 7.5-nm ASIC macrocell case study using SWCNT bundles with different ARs. In all cases, pair 1 is designed with Cu with AR of 2.1, and the other pairs are designed with SWCNT bundles (d = 1 nm,  $\beta = 1$ ). It is seen that decreasing AR, increases the number of metal pairs and the wire pitch of the pairs.

Fig. 6 shows the power dissipation and number of metal pairs versus AR. It is seen that decreasing AR from 2.1 to 0.35, decreases the total power dissipation by 41%, which means 29 W decrease in power dissipation per macrocell.

TABLE VICOMPARISON OF MULTILEVEL INTERCONNECT ARCHITECTUREDESIGN FOR T = 250, 300, and 350 K

|        |       | WCNT<br>250 K |       | WCNT<br>300 K |       | WCNT<br>350 K |

|--------|-------|---------------|-------|---------------|-------|---------------|

| Pair's | pitch | $L_{max}$     | pitch | $L_{max}$     | pitch | $L_{max}$     |

| number | [nm]  | [GP]          | [nm]  | [GP]          | [nm]  | [GP]          |

| 1      | 15    | 42            | 15    | 42            | 15    | 42            |

| 2      | 15    | 842           | 15    | 842           | 15    | 842           |

| 3      | 17.7  | 9872          | 18.1  | 9273          | 18.5  | 8737          |

| 4      | 51.8  | 34963         | 51    | 31083         | 50.6  | 27977         |

| 5      | 116.1 | 82863         | 128.5 | 82863         | 141.5 | 82863         |

## VI. TEMPERATURE VARIATION EFFECT ON n-TIER DESIGN

By technology scaling, temperature variation becomes an important issue. Borkar *et al.* [23] showed that temperature variation across a die may reach up to 50 °C. Temperature variation affects the performance of interconnects [24], so it is necessary to design multilevel interconnect architectures for acceptable performance in a temperature range. In previous sections, n-tier interconnect architectures were designed at room temperature. In this section, interconnect architecture for the macrocell is designed at T = 250, 300, and 350 K to investigate the impact of temperature variation on the design parameters. For Cu interconnects, temperature affects meanfree path and consequently the resistivity. Assuming electron free gas model for Cu, the product of bulk resistivity  $\rho_B$  and mean-free path  $\lambda_B$  is constant at all temperatures [25]

$$\rho_B(T)\lambda_B(T) = 6.6 \times 10^{-16} \ \Omega \text{m}^2.$$

(26)

Data for  $\rho_B(T)$  is given by Matula [26], so  $\lambda_B(T)$  can be computed from (26). Considering the increase in Cu resistivity due to liners, effective bulk resistivity of Cu can be obtained as

$$\rho_{\rm eff}(T) = \frac{\rho_B(T)}{\rho_B(300)} \times (2.2 \times 10^{-8}) \ \Omega {\rm m}.$$

(27)

For CNT bundles, temperature affects mean-free path, number of conducting channels, and Fermi velocity. Temperature dependence of the mean-free path was expressed in Section III. Temperature dependence of Fermi velocity is as

$$v_f(T) = v_f(300) \sqrt{\frac{T}{300}}$$

(28)

where  $v_f(300)$  is Fermi velocity at room temperature. Temperature dependence of number of conducting channels is stated in [27]. Table VI shows the multilevel interconnect architecture design for the 7.5-nm ASIC macrocell by using Cu and SWCNT bundles for T = 250, 300, and 350 K. The first pair is designed with Cu, and the other pairs are designed with SWCNT bundles ( $\beta = 1$ ). It is seen that temperature variation does not have any effect on the wire pitch and  $L_{max}$ of pairs 1 and 2. The reason is that these pairs are limited by area. Decreasing design temperature from 300 to 250 K, decreases the wire pitch of pair 5 by 10%, and the other wire pitches remain nearly constant. Increasing the design temperature from 300 to 350 K, the wire pitch of pair 5

TABLE VII Comparison of Power Dissipation and Number of Metal Pairs in Multilevel Interconnect Design for Different Temperatures

|                 | Cu-SWCNT $T = 250  K$ | Cu-SWCNT $T = 300  K$ | Cu-SWCNT $T = 350  K$ |

|-----------------|-----------------------|-----------------------|-----------------------|

| Number of pairs | 4.2215                | 4.3752                | 4.5669                |

| $P_{int}[W]$    | 33.6213               | 33.6213               | 33.6213               |

| $P_{dyn}[W]$    | 8.4792                | 13.4257               | 13.3457               |

increases by 10%. Table VII shows power dissipation and number of metal pairs of the designs. It is seen that interconnect power dissipation does not change with temperature, whereas the number of metal pairs increases by temperature slightly. Dynamic power dissipation of the repeaters at 350 K is slightly smaller than it at 300 K because of the larger wire pitches. Decreasing the temperature from 300 to 250 K, decreases dynamic power dissipation of the repeaters by 37%, because no repeater is needed in pair 2, which is of the most power hungry pairs at higher temperatures, owing to the increase in mean-free path of CNTs by 23%. So, it can be concluded that temperature variation affects higher pairs more than lower pairs. Moreover, to mitigate its impact on interconnects performance, interconnect architectures can be designed for a higher temperature (350 K). Designing the interconnect architecture for a higher temperature, increases the number of metal pairs slightly.

### VII. CONCLUSION

In this paper, n-tier methodology was developed for CNT bundle interconnects. Temperature and length domain of lowbias regime for SWCNT bundles was determined for the 7.5-nm technology node. The n-tier multilevel interconnect architecture for a 7.5-nm ASIC macrocell case study was designed using Cu and SWCNT bundle interconnects. It was shown that use of SWCNT bundles with d = 1 nm and  $\beta = 1$ reduces the number of metal pairs and power dissipation by 27% and 25%, respectively, in comparison with Cu. It was also shown that decreasing AR of SWCNT bundle interconnects in multilevel interconnect design, decreases power dissipation by 41%. Impact of temperature variation on the n-tier interconnect architectures was studied and it was shown that higher pairs are more affected by temperature variation than lower pairs. Moreover, to mitigate temperature impact on interconnects performance, interconnect architectures can be designed for a higher temperature (350K). Designing for a higher temperature, increases the number of metal pairs by 4.3%, but decreases dynamic power dissipation of repeaters by 0.6%.

#### REFERENCES

- V. Zhirnov, D. Herr, and M. Meyyappan, "Electronic applications of carbon nanotubes become closer to reality," *J. Nanoparticle Res.*, vol. 1, no. 1, pp. 151–152, 1999.

- [2] J. Li et al., "Bottom-up approach for carbon nanotube interconnects," Appl. Phys. Lett., vol. 82, no. 15, pp. 2491–2493, 2003.

- [3] W. Hoenlein *et al.*, "Carbon nanotube applications in microelectronics," *IEEE Trans. Compon. Packag. Technol.*, vol. 27, no. 4, pp. 629–634, Dec. 2004.

FARAHANI AND SARVARI: DESIGN OF n-TIER MULTILEVEL INTERCONNECT ARCHITECTURES

- [4] P. L. McEuen, M. S. Fuhrer, and H. Park, "Single-walled carbon nanotube electronics," *IEEE Trans. Nanotechnol.*, vol. 1, no. 1, pp. 78–85, Mar. 2002.

- [5] J. Hone, M. Whitney, C. Piskoti, and A. Zettl, "Thermal conductivity of single-walled carbon nanotubes," *Phys. Rev. B*, vol. 59, no. 4, p. R2514, 1999.

- [6] F. Kreupl, A. P. Graham, M. Liebau, G. S. Duesberg, R. Seidel, and E. Unger, "Carbon nanotubes for interconnect applications," in *Proc. IEEE Int. Electron Devices Meeting*, Dec. 2004, pp. 683–686.

- [7] M. Nihei *et al.*, "Electrical properties of carbon nanotube via interconnects fabricated by novel damascene process," in *Proc. IEEE IITC*, Jan. 2007, pp. 204–206.

- [8] J. Dijon et al., "Ultra-high density carbon nanotubes on Al-Cu for advanced vias," in *IEEE Int. Electron Device Meeting Tech. Dig.*, Dec. 2010, pp. 33.4.1–33.4.4.

- [9] A. Kawabata et al., "Robustness of CNT via interconnect fabricated by low temperature process over a high-density current," in *Proc. IEEE IITC*, Jun. 2008, pp. 237–239.

- [10] N. Chiodarelli, A. Fournier, H. Okuno, and J. Dijon, "Carbon nanotubes horizontal interconnects with end-bonded contacts, diameters down to 50 nm and lengths up to 20 μm," *Carbon*, vol. 60, pp. 139–145, Aug. 2013.

- [11] H. Li, W. Liu, A. M. Cassell, F. Kreupl, and K. Banerjee, "Low-resistivity long-length horizontal carbon nanotube bundles for interconnect applications—Part I: Process development," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2862–2869, Sep. 2013.

- [12] R. Venkatesan, J. A. Davis, K. A. Bowman, and J. D. Meindl, "Optimal n-tier multilevel interconnect architectures for gigascale integration (GSI)," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 9, no. 6, pp. 899–912, Dec. 2001.

- [13] J. A. Davis, V. K. De, and J. D. Meindl, "Stochastic wire-length distribution for gigascale integration (GSI)—Parts I and II," *IEEE Trans. Electron Devices*, vol. 45, no. 3, pp. 580–597, Mar. 1998.

- [14] W.-S. Zhao, G. Wang, L. Sun, W.-Y. Yin, and Y.-X. Guo, "Repeater insertion for carbon nanotube interconnects," *Micro Nano Lett.*, vol. 9, no. 5, pp. 337–339, 2014.

- [15] N. Srivastava, H. Li, F. Kreupl, and K. Banerjee, "On the applicability of single-walled carbon nanotubes as VLSI interconnects," *IEEE Trans. Nanothechnol.*, vol. 8, no. 4, pp. 542–559, Jul. 2009.

- [16] D. Patel and Y. B. Kim, "Carbon nanotube bundle interconnect: Performance evaluation, optimum repeater size and insertion for global wire," in *Proc. 53rd IEEE Int. Midwest Symp. Circuits Syst. (MWSCAS)*, Aug. 2010, pp. 749–752.

- [17] H. S. P. Wong and D. Akinwande, *Carbon Nanotube and Graphene Device Physics*. Cambridge, U.K.: Cambridge Univ. Press, 2011.

- [18] A. Naeemi and J. D. Meindl, "Physical modeling of temperature coefficient of resistance for single- and multi-wall carbon nanotube interconnects," *IEEE Electron Device Lett.*, vol. 28, no. 2, pp. 135–138, Feb. 2007.

- [19] Process Integration, Devices, and Structures (PIDS). [Online]. Available: http://public.itrs.net/reports.html, accessed 2011.

- [20] A. Naeemi and J. D. Meindl, "Impact of electron-phonon scattering on the performance of carbon nanotube interconnects for GSI," *IEEE Electron Device Lett.*, vol. 26, no. 7, pp. 476–478, Jul. 2005.

- [21] J. M. Rabaey, A. Chandrakasan, and B. Nikolic, *Digital Integrated Circuits*, 2nd ed. Upper Saddle River, NJ, USA: Prentice-Hall, 2002.

- [22] K. Banerjee and A. Mehrotra, "A power-optimal repeater insertion methodology for global interconnects in nanometer designs," *IEEE Trans. Electron Devices*, vol. 49, no. 11, pp. 2001–2007, Nov. 2002.

- [23] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, "Parameter variations and impact on circuits and microarchitecture," in *Proc. 40th Annu. Design Autom. Conf.*, 2003, pp. 338–342.

- [24] M. S. Bakir and J. D. Meindl, Integrated Interconnect Technologies for 3D Nanoelectronic Systems. Norwood, MA, USA: Artech House, 2008.

- [25] R. Waser, Nanoelectronics and Information Technology. New York, NY, USA: Wiley, 2012.

- [26] R. A. Matula, "Electrical resistivity of copper, gold, palladium, and silver," J. Phys. Chem. Ref. Data, vol. 8, no. 4, pp. 1147–1298, 1979.

- [27] A. Naeemi and J. D. Meindl, "Performance modeling for singleand multiwall carbon nanotubes as signal and power interconnects in gigascale systems," *IEEE Trans. Electron Devices*, vol. 55, no. 10, pp. 2574–2582, Oct. 2008.

**Esmat Kishani Farahani** (SM'14) received the B.Sc. and M.Sc. degrees in electrical engineering from the Iran University of Science and Technology, Tehran, Iran, and the Sharif University of Technology, Tehran, in 2006 and 2009, respectively, where she is currently pursuing the Ph.D. degree in electrical engineering with an emphasis on modeling carbon nanotubes and graphene nanoribbons for GSI interconnects.

**Reza Sarvari** (M'03) received the B.S. and M.S. degrees in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 1996 and 1998, respectively, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, GA, USA, in 2002 and 2008, respectively.

He is currently an Assistant Professor of Electrical Engineering with the Sharif University of Technology.